超大规模集成电路设计 驱动信息时代的微缩引擎

在当今这个由智能手机、高性能计算机、物联网和人工智能主导的时代,信息处理的速度与能效已成为衡量技术进步的核心标尺。而这一切的背后,都离不开一个关键的基础技术——超大规模集成电路的设计。VLSI设计是现代电子工业的基石,它决定了芯片的性能、功耗、成本与可靠性,堪称数字世界的“微缩引擎”。

一、 集成电路设计:从概念到硅片

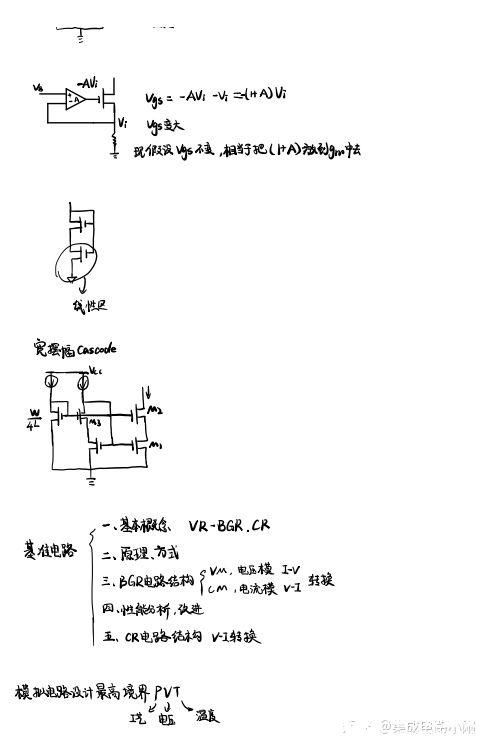

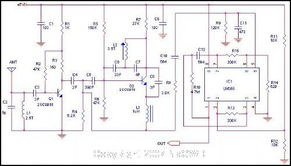

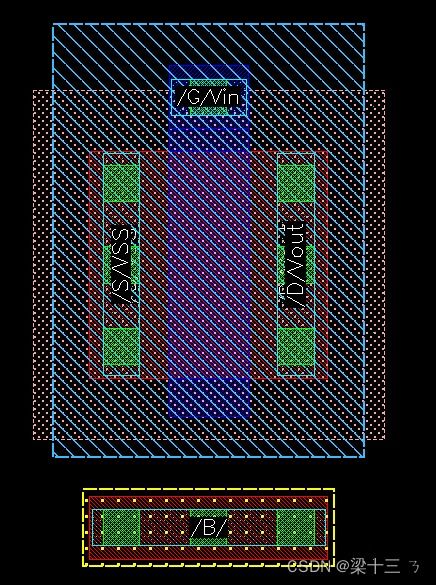

集成电路设计,本质上是将数以亿计甚至百亿计的晶体管、电阻、电容等电子元件,以及它们之间的互连线路,按照特定的逻辑功能,集成在一块微小的半导体硅片上的过程。这个过程始于一个抽象的系统需求或算法构想。设计师们首先使用硬件描述语言,如Verilog或VHDL,将所需功能转化为可执行的代码模型,这个过程称为逻辑设计。通过仿真验证功能正确后,进入物理设计阶段,即将这些逻辑门电路“摆放”在硅片上,并用“金属线”连接起来,同时要满足时序、功耗、面积和信号完整性等一系列严苛的物理约束。

二、 迈向“超大规模”:挑战与突破

当单个芯片上集成的晶体管数量超过百万、千万乃至数十亿时,便进入了超大规模集成电路的范畴。VLSI设计面临着一系列前所未有的挑战:

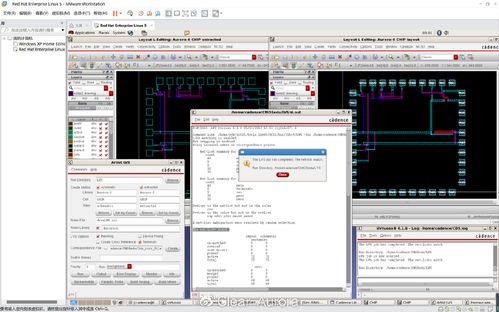

- 设计复杂性:管理数十亿个晶体管的行为和交互,如同规划一座超级大都市的交通与能源网络,任何微小的错误都可能导致整个芯片失效。这催生了高度自动化的电子设计自动化工具链,从综合、布局布线到物理验证,几乎每一步都依赖强大的算法和软件。

- 功耗与散热:“功耗墙”是制约芯片性能提升的主要瓶颈。随着晶体管尺寸缩小至纳米级,静态漏电功耗急剧增加。设计者必须采用多电压域、时钟门控、动态电压频率调节等低功耗设计技术,甚至在架构层面进行革新(如能效比更高的专用计算单元)。

- 物理极限与制程工艺:遵循摩尔定律的微缩化已接近物理极限。量子隧穿效应、工艺变异、互连线延迟成为主要障碍。为此,产业界探索了三维集成电路、新晶体管结构(如FinFET、GAA)、以及新材料(如高K金属栅、硅光子)来延续发展。

- 设计验证与可靠性:确保如此复杂的系统在制造后百分之百正确运行近乎不可能。因此,形式验证、硬件仿真、以及针对老化、软错误等可靠性问题的设计,变得至关重要。

三、 现代VLSI设计流程与范式

现代VLSI设计已形成一个高度专业化、分工细致的产业链。其核心流程包括:系统架构定义、RTL编码、功能验证、逻辑综合、可测试性设计、物理实现、时序收敛、物理验证,最终生成交付给晶圆厂的光刻掩模版图。

设计范式也在不断演进:

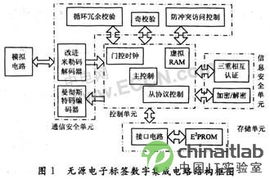

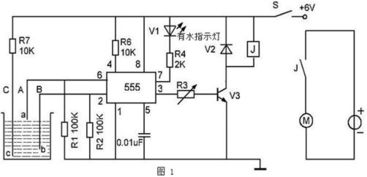

- 片上系统:将处理器核心、内存、外设接口、专用加速器等整个系统集成于单一芯片,是移动设备和嵌入式领域的标准。

- 专用集成电路与IP核复用:针对特定应用(如AI推理、密码学)设计高度优化的硬件,并通过购买或复用经过验证的IP核来大幅缩短设计周期、降低风险。

- 软硬件协同设计:特别是在人工智能和通信领域,算法、编译器与硬件架构的深度协同优化,能释放出极致的性能与能效。

四、 未来展望:超越传统,开创新局

超大规模集成电路设计正站在新的十字路口:

- 异构集成与先进封装:当单一工艺节点的提升放缓,通过先进封装技术将不同工艺、不同功能的芯片(如逻辑、内存、射频)像搭积木一样集成在一起,成为提升系统性能的关键路径。

- 设计智能化的崛起:机器学习技术正被用于优化设计流程,如预测布线拥堵、自动进行布局探索、甚至辅助进行架构设计,有望解决日益增长的设计复杂度问题。

- 面向新兴计算范式:为量子计算、类脑计算、光计算等未来计算范式设计专用的集成电路接口与控制单元,将是VLSI设计的新前沿。

###

超大规模集成电路设计,是一门融合了电子工程、计算机科学、物理学和数学的尖端艺术与工程。它不仅是将抽象思维转化为物理现实的桥梁,更是推动整个信息社会向前发展的核心驱动力。从智能手机到超级计算机,从自动驾驶汽车到云端数据中心,每一处算力的跃升与能效的优化,都镌刻着VLSI设计师们挑战物理极限、驾驭微观世界的智慧与汗水。随着技术边疆的不断拓展,这门学科必将继续引领我们步入一个更加智能、互联与高效的新时代。

如若转载,请注明出处:http://www.kxkdqntm.com/product/68.html

更新时间:2026-02-25 10:42:25