基于ISO/IEC 14443 A协议的无源电子标签数字集成电路设计

无源电子标签,作为射频识别(RFID)技术的核心组件,以其无需内置电源、体积小巧、成本低廉和寿命长久等优势,在门禁管理、物流追踪、移动支付和智能仓储等领域得到了广泛应用。其中,遵循ISO/IEC 14443 A协议的标签因其在近场通信(NFC)生态系统中的关键地位而尤为重要。本文旨在探讨基于该协议的无源电子标签的数字集成电路(IC)设计,涵盖其系统架构、关键模块设计以及面临的挑战与趋势。

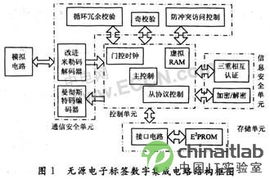

1. 系统架构概述

一个完整的基于14443 A协议的无源电子标签数字集成电路,其核心是一个超低功耗的微控制器或专用状态机。系统主要由以下几个关键数字模块构成:

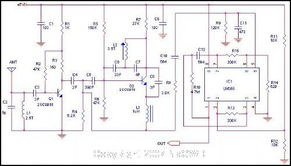

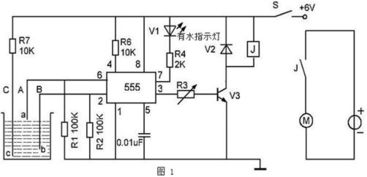

- 射频前端接口与解调器:接收来自读写器的13.56MHz载波信号,并通过包络检波等方式解调出曼彻斯特编码的数字指令。

- 时钟提取与恢复电路:从接收的射频信号中提取时钟基准,为整个数字系统提供同步时钟,通常需要处理副载波(847kHz)的时钟信息。

- 数字控制核心(状态机/微控制器):这是标签的“大脑”,负责协议层处理。它解析读写器的命令(如REQA、SELECT、HLTA等),访问存储器,并按照协议规范生成响应帧。为实现极低功耗,通常采用经过精心优化的硬连线状态机或精简指令集的8位微控制器内核。

- 存储器控制器与存储器:管理对EEPROM或铁电存储器(FRAM)的读写访问,存储唯一标识符(UID)、应用数据及系统配置信息。控制器需确保在电源波动(由射频场强弱变化引起)下的读写可靠性。

- 负载调制器:根据数字核心的指令,通过控制负载电阻的变化,将响应数据以副载波调制的形式反向散射回读写器,完成通信。

- 电源管理与复位电路:对从射频前端整流而来的不稳定电源进行稳压和滤波,并产生可靠的上电复位信号,确保数字电路在苛刻的供电条件下稳定启动和运行。

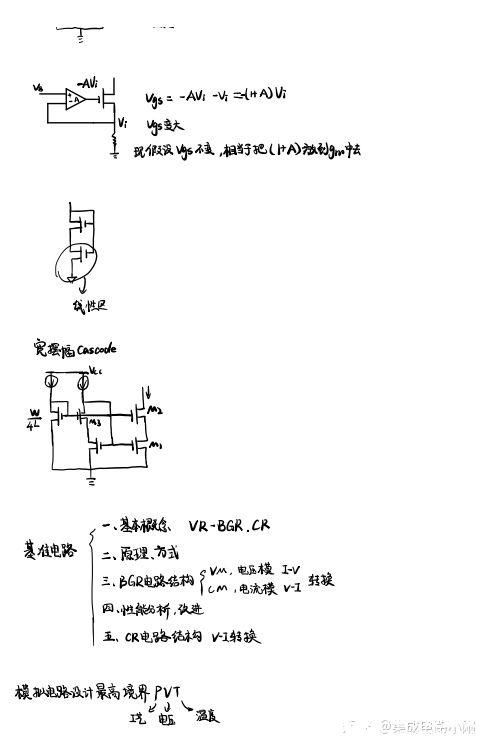

2. 关键数字模块设计考量

2.1 低功耗设计

功耗是设计的首要约束。所有数字模块必须采用低功耗设计技术:

- 亚阈值或近阈值设计:在性能允许的情况下,使晶体管工作在亚阈值区,可大幅降低动态和静态功耗。

- 时钟门控与电源门控:对非活跃模块关闭时钟甚至切断电源。

- 异步电路设计:在局部采用异步逻辑,避免全局时钟树的功耗,并能更好地适应不稳定的电源环境。

- 体系结构优化:指令集和状态机设计力求精简,减少不必要的操作和翻转活动。

2.2 协议处理状态机设计

协议处理是数字核心的核心功能。设计一个高效、确定性的状态机至关重要:

- 状态机需精确实现14443 A协议第3部分(初始化和防冲突)及第4部分(传输协议)所规定的流程。

- 需要正确处理位级定时(如帧延迟时间FDT),这通常需要一个精密的定时器模块。

- 防冲突算法(位帧防冲突)需要硬件加速支持,以实现快速的UID识别和选择。

2.3 存储器接口的可靠性设计

由于无源标签的电源完全依赖外部射频场,可能在读写操作期间发生波动甚至中断。因此:

- 存储器控制器需要实现原子操作和掉电保护机制,例如,在写操作前将数据和地址暂存于易失性寄存器,并采用“写-校验”序列,防止数据损坏。

- 对于EEPROM,需精确控制高压产生电路和编程时序。

2.4 抗干扰与鲁棒性设计

标签工作在复杂的电磁环境中,数字电路必须具备抗干扰能力:

- 对来自模拟前端的解调数据,需要进行数字滤波和毛刺消除。

- 复位电路需具有足够的迟滞,防止电源轻微波动导致系统反复复位。

- 采用差错检测机制(如CRC校验),确保命令和数据的完整性。

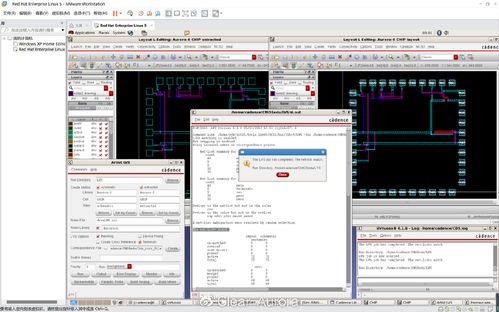

3. 设计流程与验证

设计流程通常遵循标准的数字IC设计流程:

- 系统建模与算法验证:使用高级语言(如C/Matlab)对协议处理算法和系统行为进行建模和验证。

- 寄存器传输级(RTL)设计:使用硬件描述语言(如Verilog HDL)编写所有数字模块的代码,重点在于低功耗描述。

- 功能仿真与综合:进行大规模的功能仿真以验证协议符合性,然后使用综合工具将RTL代码映射到目标工艺库,并施加严格的面积和功耗约束。

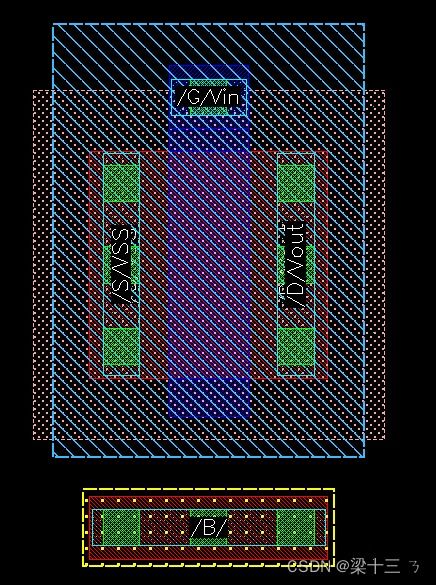

- 后端物理设计:包括布局布线、时钟树综合、电源规划等。需要特别关注模拟-数字混合信号的布局隔离,防止噪声耦合。

- 后仿真与验证:提取寄生参数后进行带时序信息的门级仿真,以及最终的物理验证(DRC, LVS)。

4. 挑战与未来趋势

- 功耗的极致降低:随着应用场景的拓展(如嵌入式传感标签),对功耗的要求越发严苛,需要探索更先进的电路技术和新材料。

- 安全性增强:集成轻量级的密码算法硬件加速引擎(如AES, ECC),以应对日益增长的安全需求,同时不能显著增加功耗和面积。

- 系统集成度:向更先进的工艺节点(如55nm, 40nm)迁移,以集成更多功能(传感器接口、能量收集管理)并进一步降低成本。

- 设计自动化:开发针对超低功耗、不稳定电源环境的设计工具和标准单元库,提升设计效率。

结论

基于ISO/IEC 14443 A协议的无源电子标签数字集成电路设计是一个多学科交叉的工程挑战,它平衡了协议复杂性、极致的功耗约束、成本控制和可靠性要求。通过精心的系统架构规划、创新的低功耗电路设计以及严谨的设计验证流程,能够实现高性能、高可靠性的标签芯片,为物联网的末梢节点提供关键的感知与识别能力。随着工艺进步和设计方法学的创新,未来的无源标签芯片将变得更智能、更安全、更节能。

如若转载,请注明出处:http://www.kxkdqntm.com/product/67.html

更新时间:2026-02-25 16:53:21