CMOS模拟集成电路设计 现代电子系统的基石

在当今高度数字化的世界中,模拟集成电路(Analog Integrated Circuits, ICs)仍然是连接真实物理世界与数字处理核心的不可或缺的桥梁。其中,互补金属氧化物半导体(CMOS)技术,凭借其低功耗、高集成度和成熟的制造工艺,已成为模拟集成电路设计的主流选择。CMOS模拟集成电路设计,是一门融合了半导体物理、电路理论、系统架构与工艺技术的综合性艺术与科学。

CMOS技术的优势与挑战

CMOS工艺最初是为数字电路(如微处理器和存储器)开发的,其核心是同时使用N型和P型MOSFET(金属氧化物半导体场效应晶体管)。这种结构使得数字电路在静态时功耗极低。当这项技术被应用于模拟电路设计时,它带来了革命性的变化:模拟功能模块可以与庞大的数字系统(如处理器、存储器、逻辑控制单元)集成在同一块芯片上,从而诞生了复杂的“片上系统”(System-on-Chip, SoC)。这极大地降低了系统成本、体积和功耗,并提高了可靠性。

将CMOS工艺用于模拟设计也面临诸多挑战。与数字电路主要关注“0”和“1”的开关特性不同,模拟电路处理的是连续变化的电压或电流信号,对晶体管的跨导、输出阻抗、噪声、匹配精度、线性度以及电源电压抑制比等参数极为敏感。在先进工艺节点下,晶体管尺寸不断缩小,电源电压持续降低,这使得设计高性能的模拟模块(如高增益运放、高精度数据转换器、低噪声放大器)变得愈发困难。

核心设计流程与模块

一个典型的CMOS模拟集成电路设计流程始于明确的系统规格定义,包括增益、带宽、噪声、功耗、线性度、面积等指标。设计师会进行架构选择,确定是采用全差分结构、开关电容技术还是连续时间方案等。

在电路级设计阶段,设计师需要精心设计核心的模拟构建模块:

- 运算放大器(Op-Amp): 这是模拟电路中最基本且关键的模块,其性能直接影响滤波器、数据转换器等子系统的表现。设计重点包括高增益(通常采用共源共栅或增益自举技术)、高带宽、足够的相位裕度以确保稳定性,以及低噪声和低失调。

- 基准电压源与电流源: 为整个芯片提供稳定、与电源电压和温度变化无关的参考。带隙基准源是其中的经典结构,其设计关键在于实现正负温度系数的精确补偿。

- 数据转换器: 包括模数转换器(ADC)和数模转换器(DAC),是连接模拟与数字域的咽喉要道。设计涉及对速度、精度、功耗的极致权衡,常见结构有逐次逼近型、流水线型、Σ-Δ型等。

- 锁相环: 用于产生稳定时钟或进行频率综合,由压控振荡器、鉴频鉴相器、电荷泵和分频器等组成,设计难点在于低相位噪声和低抖动的实现。

完成电路设计后,需进行细致的仿真验证,包括直流工作点分析、交流小信号分析、瞬态分析、噪声分析、蒙特卡洛统计分析(评估工艺偏差的影响)等。之后进入版图设计阶段,这是将电路图转化为实际制造掩膜版图的过程。模拟版图设计尤其讲究,需要特别注意器件的匹配、信号路径的隔离、寄生效应(如寄生电容和电阻)的最小化,以及电源/地的噪声抑制。

未来趋势与展望

随着物联网、人工智能、生物医疗电子和汽车电子等领域的飞速发展,对CMOS模拟集成电路提出了更高要求:更低的功耗以延长电池寿命(例如用于可穿戴设备)、更高的精度和动态范围(例如用于传感器接口)、更宽的带宽(例如用于5G/6G通信),以及更强的鲁棒性以适应恶劣环境。

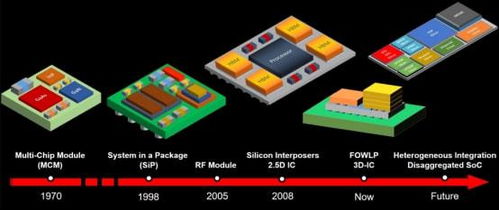

新技术的融合也在开辟新路径。例如,利用先进CMOS工艺中的数字辅助技术来校准和补偿模拟电路的固有缺陷;探索超越传统硅基CMOS的材料(如锗硅、III-V族化合物)以提升高频性能;以及向三维集成发展,通过芯片堆叠实现异质集成,突破平面集成的限制。

总而言之,CMOS模拟集成电路设计是电子工程领域的核心与前沿。它要求设计师不仅要有扎实的理论功底和丰富的实践经验,更需具备深刻的洞察力和创新思维,在工艺约束、性能指标和设计成本之间找到精妙的平衡点,从而持续推动着整个电子信息产业向前发展。

如若转载,请注明出处:http://www.kxkdqntm.com/product/53.html

更新时间:2026-02-25 17:56:37